- Designated for high demands regarding bandwidth, timing, and precision

- Specialized NAT-MCH-CLK-PHYS mezzanine module

- Power and system management for up to 12 AMCs, 2 CUs, and 4 PMs

- PCIe Gen3 x16 data switching towards backplane and front uplink

- RTM with COMExpress Support

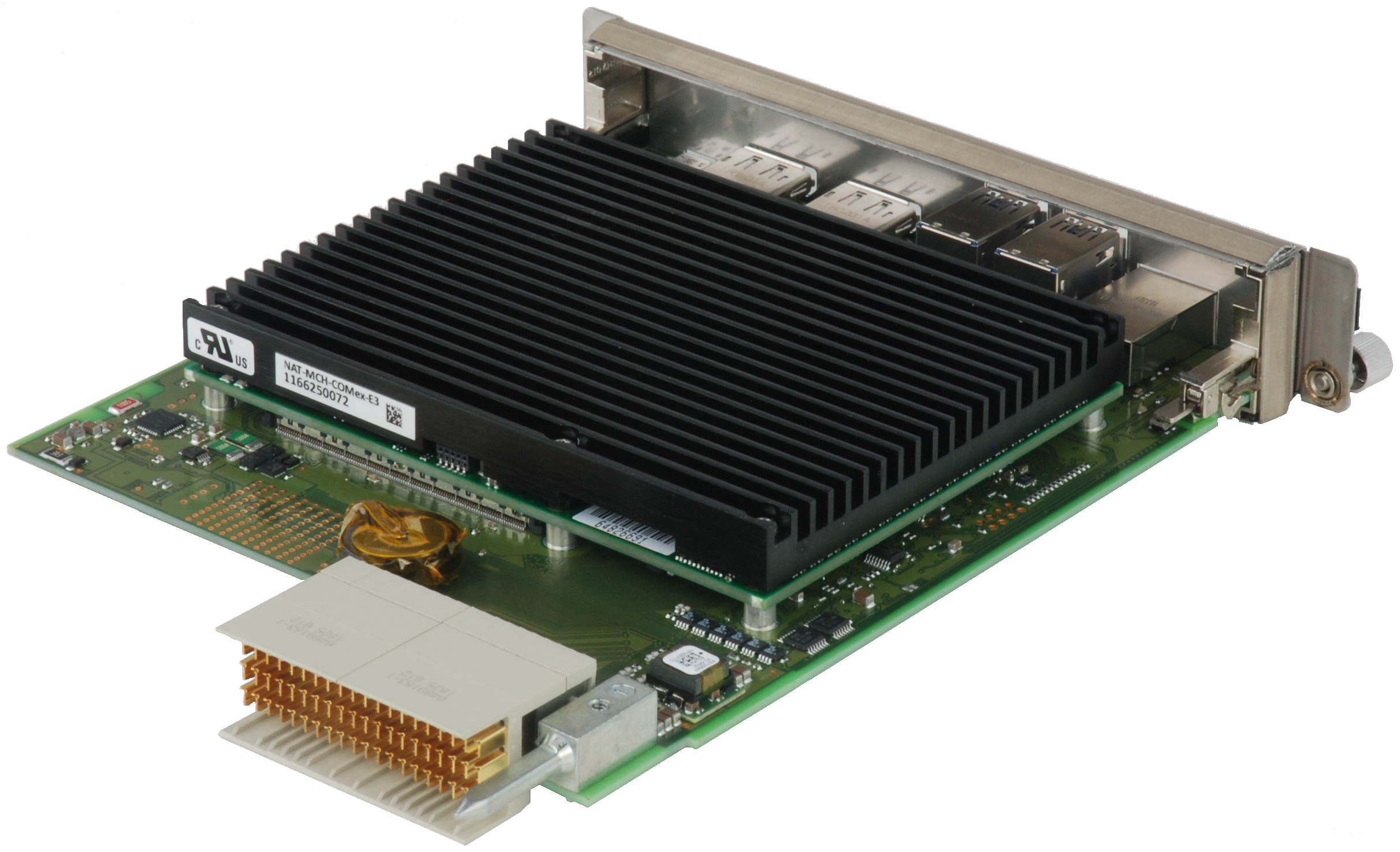

NAT-MCH-PHYS80

Double-width MTCA Carrier Hub for physics applications

- Designated for high demands regarding bandwidth, timing, and precision

- Specialized NAT-MCH-CLK-PHYS mezzanine module

- Power and system management for up to 12 AMCs, 2 CUs, and 4 PMs

- PCIe Gen3 x16 data switching towards backplane and front uplink

- RTM with COMExpress Support

Description

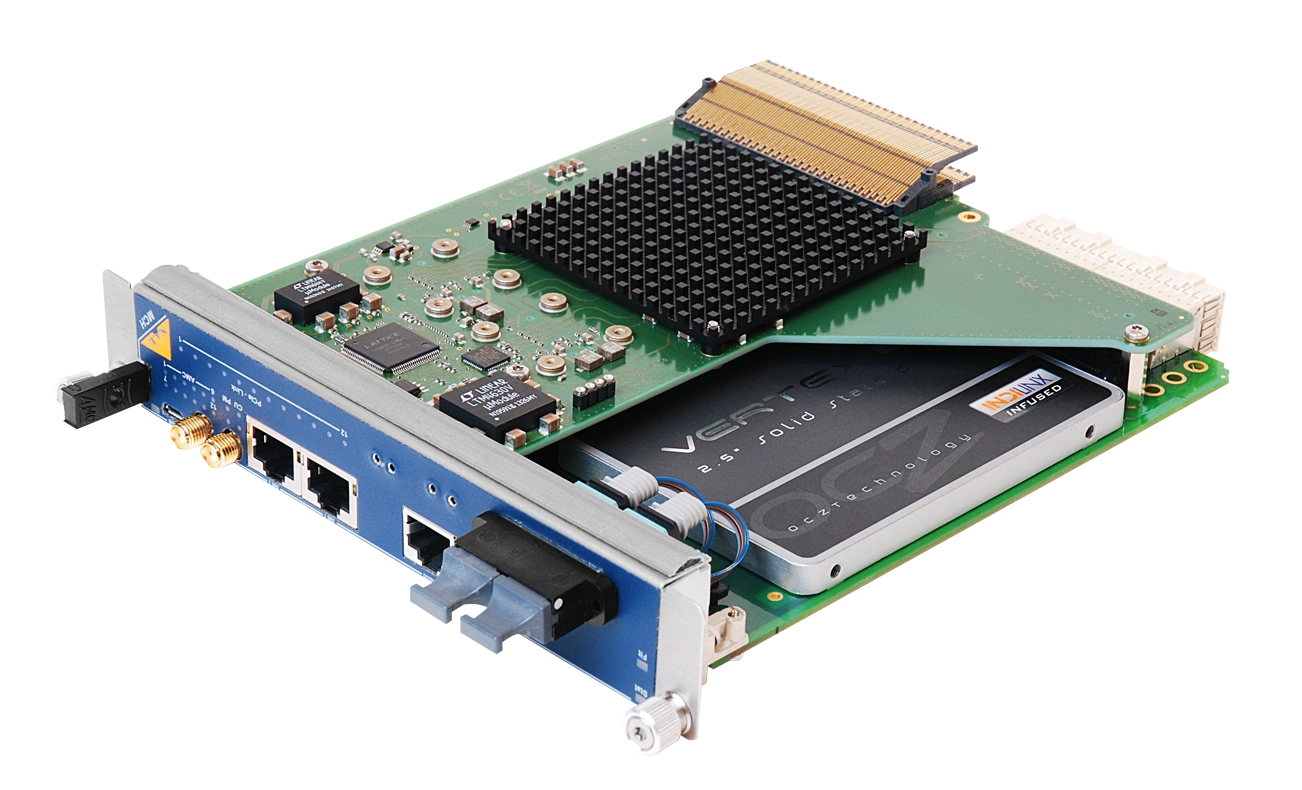

The NAT-MCH-PHYS and NAT-MCH-PHYS80 are MTCA Carrier Hubs in double-width, full-size form factor for any MTCA.4 system. As the name suggests, these MCH variants target on physics applications, but nevertheless fit perfectly for other tasks with high demands regarding bandwidth, timing, and precision.

Basically, both variants comprise a base module (named NAT-MCH-M4) and a special clock module for physics applications. Main difference between both options is the type of the PCI Express HUB-Module and support of RTM ( Rear Transition Modules) functionality.

All variants of the NAT-MCH serve as central management and data switching entity for an MTCA system. They offer power and system management for up to 12 AMCs (13 in a non-redundant system without 2nd MCH). Moreover, they support up to two Cooling Units and up to four Power Modules in various (redundant) configurations.

The double-width base module NAT-MCH-M4 is the ideal choice for a MTCA.4 system, whereas its single-width brother NAT-MCH aims for applications in MTCA.0 form factor. Functionally, both variants are identical in most parts. The NAT-MCH-M4 however provides the option for a Zone3 connector and mounting space for two SATA-HDDs. Both of them are useable in combination with an optional NAT-MCH-RTM.

Both base modules offer Gigabit Ethernet supporting port-based and tagged VLAN, Rapid Spanning Tree, as well as a port-based rate control via Fabric A. They also provide uplink ports on the front panel to interconnect to other systems.

For advanced clocking switching and distribution, a separate clock module is mounted on the MCH base board. The NAT-MCH-CLK-PHYS mezzanine is a specialized low-jitter clock module for physics applications. Nevertheless, it is also an option for other tasks requiring low-jitter and low-latency clock functionality.

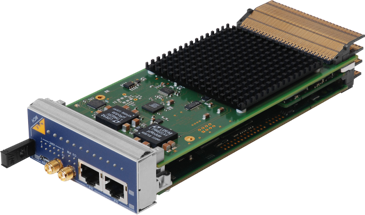

NAT-MCH-PHYS

The NAT-MCH-PHYS owns an NAT-MCH-PCIEx48 HUB-Module. It provides an PCIe Gen3 x1/x4 link to each of the 12 AMCs in an MTCA system. The PCIe chipsets provide a quality of service (QoS) module and are configurable in terms of a non-transparent port for multi-host support.

The HUB-Module supports full non-transparent bridging functionality to allow implementation of multi-host systems and intelligent I/O modules. Moreover, it provides clustering support for six independent clusters with one configurable non-transparent upstream port. Each cluster offers its own transparent upstream port.

The NAT-MCH-PHYS does not support RTM functionality.

NAT-MCH-PHYS80

This variant comprises the NAT-MCH-PCIex80 HUB-Module. It features an PCIe Gen3 x1/x4 link to each of the 12 AMCs in an MTCA system. Optical front uplink functionality is available as an option. Depending on the chosen variant, the NAT-MCH-PCIex80 comes with one (x8) or two (x16) optical transceivers. So with the x8 variant, one PCIe Gen3 x8 link is available at the front panel. Choosing x16 allows for two x8 or one x16 connection.

If a NAT-MCH-RTM is attached to the MCH, it can be supplied by another PCIe Gen3 x16 connection.

As the NAT-MCH-PHYS80 supports RTMs, it offers the possibility to connect to a µRTM-Backplane, the NAT-LLRF-Backplane. This backplane is an auxiliary backplane which is mounted behind the standard MTCA.4 backplane and allows to interconnect directly to RTMs.

Key Features

CPU and Memory

IPMI and Compliance

Supported Fabrics and Compliance

Fabric A: GigaBit Ethernet switching

Fabrics D-G: PCIe Gen3

- X1 or x4 to 12 AMCs

- One x16 or two x8 to optical uplink (optional)

- x16 to RTM or to one AMC slot (requires backplane support)

Clock Distribution with NAT-MCH-CLK-PHYS

- CLK1 and CLK2 by special low jitter and low latency circuitry (NAT-MCH-CLK-PHYS)

- CLK3 fixed mean 100MHz PCIe clock (HCSL)

Carrier Management

- Management of up to 13 AMCs, 4 Cooling Units, and 1-4 Power Modules

- Supports redundant architectures and fail-over procedure

- Support configurable emergency shutdown of AMCs or entire system

Shelf and System Manager

- For detached or stand-alone operation both managers are available on-board, hook-in for external managers via 1GbE port at front panel

Operating System and API

Indicator LEDs

- 3 standard AMC LEDs

- 12 bi-colored LEDs for AMC slot states

- 2 bi-colored LEDs for Cooling Units

- 4 bi-colored LEDs for Power Modules

- 13 bi-colored LEDs for PCIe link status (failed, Gen1, Gen2, or Gen3)

Front Panel Connectors

- 2x 1GbE for management connection and Fabric A system up-link (load sharing supported)

- External clock reference (bi-directional)

- Serial and USB debug connector (console)

- Fabric D-G uplink (two x8 or one x16)

Related Products

Order Codes

NAT-MCH-[Option]

| -PHYS |

Double, full-size NAT-MCH with 16 port GbE switch, 48 port PCIe Gen3, and CLK-PHYS module |

| -PHYS80 |

Double, full-size NAT-MCH with 16 port GbE switch, 80 port PCIe Gen3, and CLK-PHYS module |

Front Uplink

| -PCIEx8-O-UPLNK |

like -PHYS80 with additional eight optical uplinks for PCIe |

| -PCIEx16-O-UPLNK |

like -PHYS80 with additional sixteen optical uplinks (either two x8 or one x16) for PCIe |

Accessories

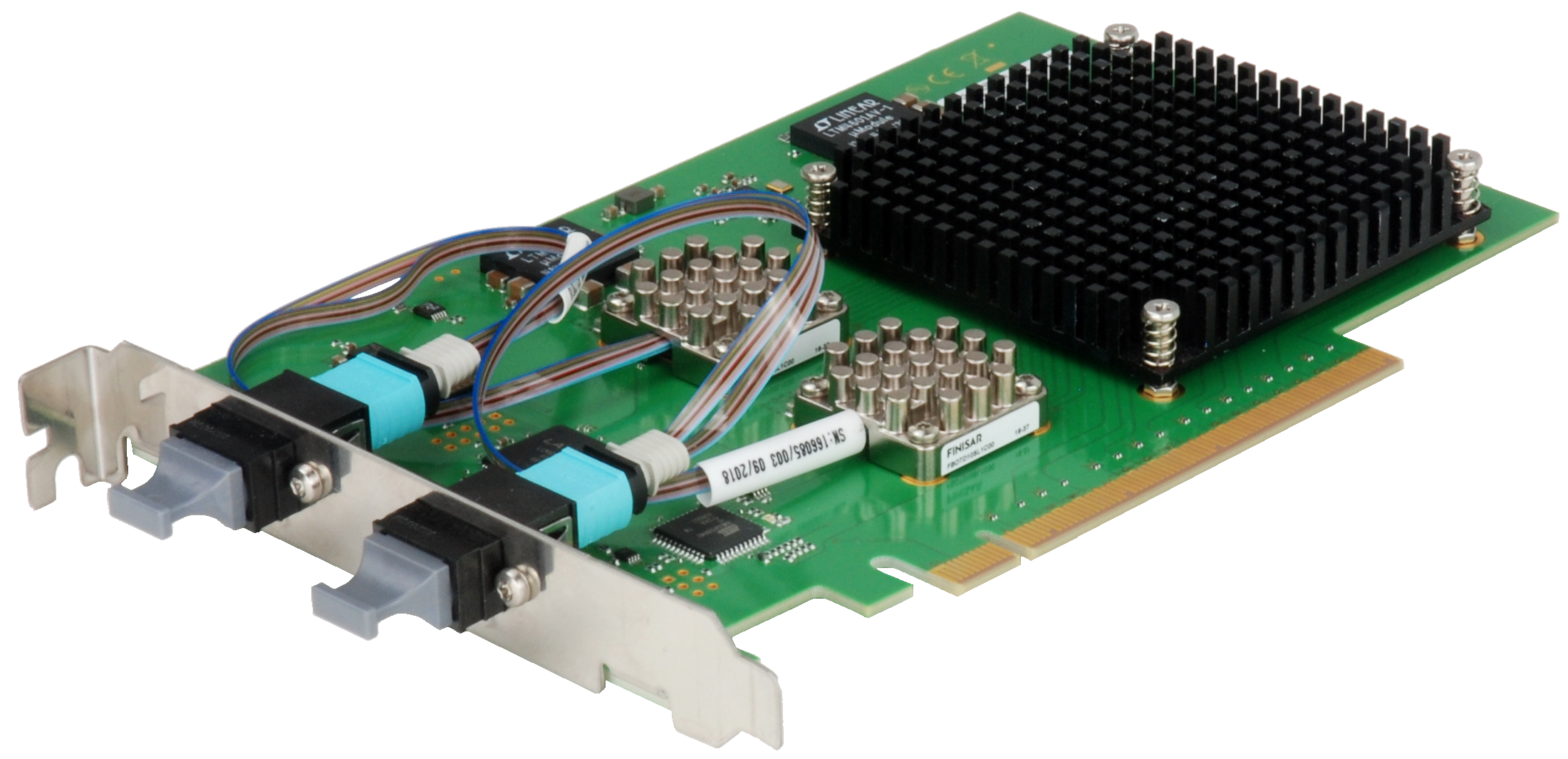

| NAT-MCH-PCIECABO | fibre uplink cable for PCIe uplink |

|

NPCIe-Uplink-O-x8 |

PCIe card terminating PCIe uplink |

Solutions / Applications

- High energy physics

- Telecommunication

- Energy industry

- Industrial automation

- Civil aviation

- Research and development

- Any other MTCA.4 application with high demands on precision and timing